基(jī)於 SOPC 技術和模糊控製理(lǐ)論的數控機床控製係統的設計

2018-5-23 來(lái)源: 柳州鐵道職業技術學院 作者:覃莉莉

[摘要]本文提出(chū)了一種基(jī)於 SOPC 技術和模糊控製(zhì)理論的數控機床 XY 工作台控製係(xì)統解決方(fāng)案,通過Quartus II、Nioses II IDE 和 SOPC Builder 等(děng)整套開發工具完成了(le) SOPC 係統的開發。

[關鍵詞]數控機床;控製係統;模糊控製理論;SOPC;Nioses II

SOPC(System On a Programmable Chip),是在一塊矽片上利用可(kě)編程邏輯控製技術集成整個係統(tǒng)的一項技術。SOPC 可以用來進行電子信息處理和嵌入式係統的設計。本文設計的數控機床控(kòng)製係統中(zhōng)是基於 FPGA嵌入 IP 軟核的應用。

一、SOPC 係(xì)統的設計

SOPC(System On a Programmable Chip)利用一個芯片就可以(yǐ)完成全部(bù)的邏輯處理,其硬(yìng)件采用 FPGA。這種(zhǒng)微處理器(qì)係統采用(yòng)嵌入式的結(jié)構設計。

建立在 SOPC 技術基礎上的 Nioses II 處理器是一種 32 位的 RISC 處(chù)理器軟內核。可以完成 SOPC 係統開發(fā)的整套(tào)工具,目前市場上主要(yào)有(yǒu) Nioses II IDE、SOPC Builder 以及

Quartus II等。典(diǎn)型的 Nioses II 的微控製器包含 Avalon 總線、I/O 控製器、微處理器內核、定時器、存儲器控(kòng)製單元和必要的外圍控製部分。

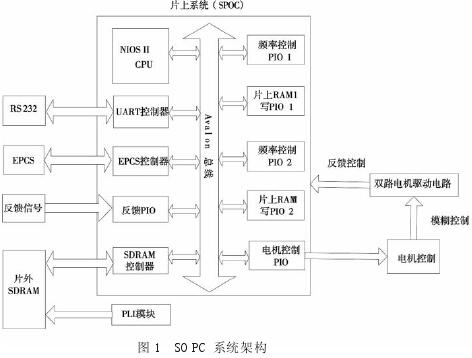

圖 1 所示的(de) SOPC 係統架構是基於(yú)數控機床控製係統的要求而設計的.

二、定製 Nioses II 微控製器軟核(hé)

根據數控係統的控製要求,本文對 Nioses II 微控製器軟核進行了配置。這個配置包括:中央處理器模塊、SDRAM控製(zhì)模塊、UART 控製(zhì)模(mó)塊、EPCS 控製模塊、反饋模塊,頻率發生(shēng)控製器(qì)、RAM 寫入模(mó)塊以及電機控製模塊。其定製過程如下:

(1)構建(jiàn)係統軟(ruǎn)核在 SOPC Builder 界麵(miàn)中,根據 SOPC 係統架構構建係統軟核,設定係(xì)統(tǒng)時鍾頻率為 50MHz。本係統對要求具備高速的響應速度(dù),因此在 NiosesⅡ CPU 的三種類(lèi)型中選擇快速型 NiosesⅡ/f 的(de)軟核類型。JATG 調試模塊在係(xì)統運行的過程中將占用較多的係(xì)統資源,為了確保係統調試能順利地加入 JATG,減少係統所占用的軟(ruǎn)硬件(jiàn)資源,需要在(zài)完成係統的調試之後,把(bǎ) debugging level 設置為 No Debugger。

(2)建立 SDRAM 模塊SDRAM 諸如刷新 、初始化等邏輯控製由(yóu) SDRAM 控製器來實現。物理層麵上 FPGA 跟 SDRAM是連接在一起的,SDRAM 控(kòng)製(zhì)器的參(cān)數(shù)設定如下:行地(dì)址(

Row address)12 位,列地址(Column address )8位,數據位寬(Data width)16 位。通過 SDRAM 控製器將 SDRAM 用作(zuò)大容量存儲器。

(3)建立 EPCS 控製(zhì)器:EPCS用於存儲 FPGA 配置數據和 Nioses II程序代碼。

(4)建(jiàn)立 JTAG UART 控製(zhì)器:JTAG UART 用於Nioses II 應用程(chéng)序的調試。

(5)建(jiàn)立 UART 控製器:RS232的時序議利用異步收發器(UART)控製器來實現。其功能在於提供波特率,且波特率可以(yǐ)根據需(xū)要進行調節。訪問 UART 模塊,在 Nioses II

係統中,利用 Avalon 總線可以很容易實現,Avalon 總線允許 Avalon 主外設(例如(rú) Nioses II 處理器)通過簡(jiǎn)單(dān)的讀和寫(xiě)控(kòng)製寄存器以及數據寄存器(qì)與該 UART 核實現通信。

設置串口通信波特率為 19200,停止(zhǐ)位 1 位,數據位8 位,沒有奇偶性的檢驗。

(6)建立係統 ID 外設:生成 Nioses II 係統(tǒng)時,會配置唯一的 ID 號,並存入 System ID 寄存(cún)器,用以鑒定(dìng) NiosesII 程序是否與係統匹(pǐ)配。如不匹配,程序將無法下載到

Nioses II 係統。

(7)添加 PIO 接口,所添(tiān)加的 PIO 接口主要包括:RAM寫PIO、反饋 PIO、行(háng)程(chéng)開關 PIO、加入電機運行參數 PIO(輸出類型)、基準頻率控製 PIO、開(kāi)始控製 PIO。最後生成 Nioses II 係統。

三(sān)、係統核外邏輯(jí)的設(shè)計與構建

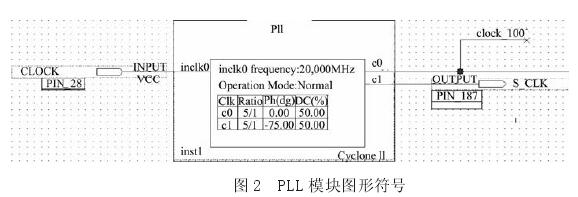

(1)鎖(suǒ)相環(huán) PLL 模塊的建立鎖相環的功能在於解決係統各種設備間的時鍾同步問題。它可以實現延時(shí)的功能,調節時鍾信號。鎖相環的設計對於整個係統(tǒng)而言,意義重(chóng)大。本設計中為 Nois II 軟核(hé)提供時鍾的是 20MHz 的有源晶振,這個晶振(zhèn)外接在 FPGA 上。把有源晶振的倍頻設定在 100MHz(c0)。為 SDRAM 提供同樣頻率(lǜ)時鍾的是圖 2 中所設計的 PLL 的 c1。其頻率(lǜ)的設定跟有源晶振的頻率一致(zhì),偏移量取-75deg。

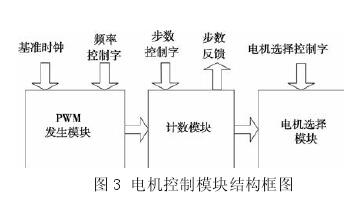

(2)電機控製模塊電機控(kòng)製模塊主要由(yóu) PWM 發生模塊、計數模塊和電(diàn)機選擇模塊構(gòu)成,如圖 3 為其結構框圖。

四、相關硬件電路設計

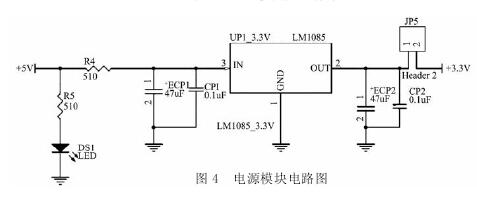

1.電源模塊(kuài)電源模塊是保證嵌入(rù)式係統工作(zuò)的前提條件之一,在本係統中,電源模塊主要負責給 FPGA 以及後續的電路供電(diàn),使用 LM1085_3.3V 來實現從 5V 轉到(dào) 3.3V,並且在輸入端和輸出端加濾(lǜ)波電容,保證供(gòng)電穩定。圖 4 為電源模塊(kuài)電路(lù)圖。

2.速度檢測反饋電路

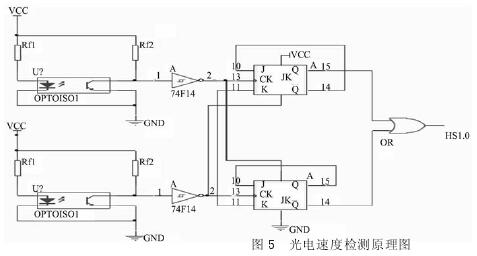

光電編碼盤角度檢(jiǎn)測傳感(gǎn)器是一種(zhǒng)廣泛應用的編碼式(shì)數字傳(chuán)感器(qì),它將測得的角(jiǎo)度位移(yí)轉換為脈衝形式的數(shù)字信號輸出。其(qí)電路原理圖見圖 5 所示。

3.電機驅動電路

驅動電路開(kāi)關管選用(yòng)絕緣柵型功率管(guǎn) IGBT。本(běn)係統 選 用 美 國(guó) SGS 公 司(sī) 生 產 的 專 用(yòng) 集 成 驅 動 芯 片PBL3717。該芯片構建的電路,不同於傳統分離元件(jiàn)組成的電路,避免了工作電路複雜、使用元件多、開啟和關斷時間長等缺點。PBL3717 柵極驅動(dòng)器能夠在驅動一個高壓(yā)側的同時,驅動一個低壓(yā)側的功率 MOSFET,能夠在一個高性能(néng)的封裝裏實現大部分(fèn)的功能。

在設計時,隻需要添加一路控(kòng)製電源和少量分立元件即可。PBL3717 芯片即可采用自(zì)舉自容實現(xiàn) MOSFET 的驅動。其導通/關斷時間為120/94ns,驅動能力為(wéi) I0+/-=3A/3A,偏值電壓可達500V,開關頻率可以從數十(shí)赫茲達數百千赫茲,同時PBL3717還具有欠壓告警、欠壓封鎖、過流保護(hù)之功能等比較完善的保護功能(néng)。所以驅動電路選用 2 片 PBL3717 驅動兩個 H 橋。

4.係統複位電路

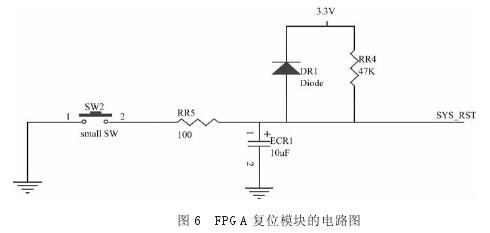

根(gēn)據(jù)數控係統的控(kòng)製需求,本設計需要把處理器嵌入到 FPGA 內部。而 FPGA 在(zài)每次配置的加載都會被複位,這樣的複位自動進行。基於這樣的情況,需要設計一個係統的複位電路,把 FPGA 內部的狀(zhuàng)態初始化。

在本設計中,人為(wéi)地(dì)幹預係統的運行,必(bì)要時,重新輸入參數是(shì)必需的要(yào)求。為實現這樣的要求,必須設計一個複位電路,這個複位電路可以(yǐ)通過手動的方式實現控製。按照低電平有效抗幹擾(rǎo)能力更強的原則,如圖 6 所本文設計了一個常態為高電平(3.3V),通過按鍵來拉低信號(hào)複位電路.

五、自整定模糊 PID 控製器(qì)設計

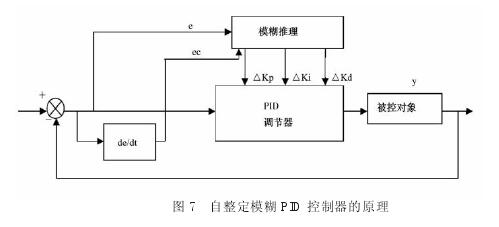

輸入誤差 e 以及誤差的變化 ec,來構建自整定(dìng)模糊PID 控製器。通過算法,設計模糊(hú)控製的規則,修改 PID參數,原理如圖 7 所示.

從係統響應速度、穩定與(yǔ)否、穩定精度如(rú)何(hé)以及超調量等方麵來考慮,Kp′,Ki′,Kd′的(de)作用為:

(1)響(xiǎng)應速度慢,調節精度低,係(xì)統穩態、動態特性差。通常的原因(yīn)是(shì) Kp值取得過小。增大 Kp的(de)取值可以解決上述問題。

(2)Ki能夠消除係統穩態誤差。Ki越大,則係統靜態誤差越快(kuài)消除。這個參數(shù)取得過大,容(róng)易(yì)產生響應初期積(jī)分飽和的現(xiàn)象,從(cóng)而造成響應過程的較大超調;但取得過小,係統靜態誤差難以消除,對係統調節精度產生不利的影響。

(3)要想獲得良好的係(xì)統動態特性,可以取(qǔ)較(jiào)大的Kd值。但是 Kd過大,會(huì)造成調(diào)節時間的延長。發(fā)生響應過程的提前製動,對(duì)於係統額抗幹擾性能也會造成(chéng)不利的影響。

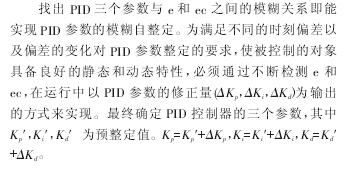

這個參數(shù)的作用在於使係統得到較好的動態特性(xìng),對響應中偏差(chà)變化的任意性進(jìn)行抑製,還可以對(duì)偏差變(biàn)化的(de)方向進行預報。綜合(hé)對係統輸出產生(shēng)影響的三大參數參數 Kp、Ki和(hé) Kd,不難歸納出,在不同的 e 和 ec 下(xià),受控參數 Kp、Ki 和(hé) Kd 的自(zì)整定要求(qiú),得出模糊控製規則的語言描述:

PID 控製器參數(shù) Kp,Ki,Kd 的整定要求因(yīn)偏差 e 和偏差變化率 ec 的不同而異,分述如下:

(1)當 e 較(jiào)大時,取較大的 Kp,可以提(tí)高係統相應速度;需要注(zhù)意的是,微(wēi)分飽和的最直接原因(yīn)是開偏差 e 在(zài)開始的瞬間變大(dà)。微分飽和所帶來的(de)影響會造成控製作用超出許可的範圍。此時,可以選選取較小的 Kd。積(jī)分飽和是控製係統所不希望出現的結果(guǒ),為了避免這種情況的產(chǎn)生,可以取 Ki=0 限製積分(fèn)的作用。

(2)e 處於中等大小時,Kp 取得小些,容易獲得(dé)係統響應較小的超調性(xìng)。這個(gè)時候,應該取適當(dāng)的 Ki 值。此時,對係統影響較大的是 Kd 的取值,為保證係統的響應速度,這(zhè)個參數取值要適中。

(3)偏差 e 接近設定值,數值較小時,為(wéi)了獲得係統良好的(de)穩定特性,需要增加 Kp 和 Ki 的取(qǔ)值。震蕩(dàng)的產(chǎn)生容易出(chū)現在在係統(tǒng)設定值附近。為了減少這個問題帶來的不利影(yǐng)響,需要增強係統的抗幹擾性能。當 ec 較大時,Kd 應取小些;當 ec 較小時,Kd 可取值大些。

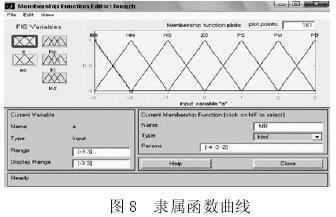

圖 8 為隸屬度函數曲線。

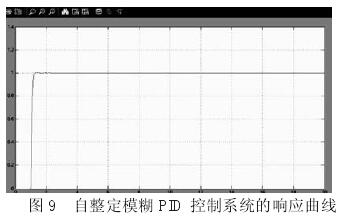

圖(tú) 9 所示為使用 Matlab 進行仿真所得到(dào)的自整定模糊(hú) PID 控製係(xì)統響應曲線(xiàn)。仿真的結果表明,采用自整定模糊 PID 控製,係統的穩(wěn)態性能好,調節(jiē)精度提高,響應速度快,且沒(méi)有超振蕩和超調。

現代社會經(jīng)濟和技術發展迅(xùn)速,各種裝備(bèi)都(dōu)在不斷進行升級,因而對於設備的要求也在(zài)不斷提高,研究數控(kòng)機床的(de)相關控製技術有著非常重要(yào)的意義。基(jī)於SOPC 技術和模糊控製理(lǐ)論的數控機床控製係統(tǒng),開發周期短,成本低廉,是一個值得深入探討的研(yán)究方向。

投稿箱:

如果(guǒ)您有機床行業、企業相關新聞稿件發表,或進行資訊合作(zuò),歡迎聯係本網編輯部, 郵箱:skjcsc@vip.sina.com

如果(guǒ)您有機床行業、企業相關新聞稿件發表,或進行資訊合作(zuò),歡迎聯係本網編輯部, 郵箱:skjcsc@vip.sina.com

更多相關信息

業界視點

| 更(gèng)多

行業數(shù)據

| 更多

- 2024年11月 金屬切削(xuē)機床產量數據

- 2024年11月 分地區金屬切削(xuē)機(jī)床產量數據(jù)

- 2024年11月 軸承出口情況

- 2024年11月 基本型乘用車(轎車)產量數(shù)據

- 2024年11月 新能源汽車產量數據

- 2024年11月 新能源汽車銷量情況

- 2024年10月 新能源汽車產量(liàng)數據

- 2024年(nián)10月 軸承(chéng)出口情況

- 2024年10月 分地區金屬切削機(jī)床產量數據

- 2024年(nián)10月 金(jīn)屬切削機床產量數據

- 2024年9月 新能源汽車銷量情況

- 2024年8月 新能源汽車產量數據

- 2028年8月 基本型乘用車(轎車)產量數據

博(bó)文選萃

| 更多