成熟的PCIe 6.0 IP可極大降低複雜係統開發難度

2022-5-26 來源:Cadence 作者:-

從正式發布至今,PCI Express®(PCIe®)發展迅速,在現代(dài)數字世界中(zhōng)無處不在,已經成為高性能計算、人工智能/機器學習(ML)加速器、網(wǎng)絡適配器和固態(tài)存儲等應用不可(kě)或缺的一項技術。不僅如此,PCIe技(jì)術近(jìn)期在速度(dù)和延遲方麵取得的突(tū)破讓其在存儲器架構中也獲得(dé)了廣泛應用(例如通過PCIe/CXL插槽連接的持久內存和DRAM)。

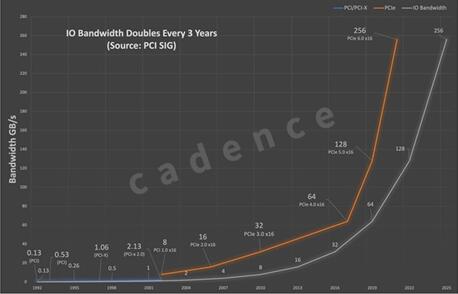

人工智能/機器學習(ML)應用的變革以及企業工作(zuò)負載加速遷移至雲端的趨勢,持續推動數(shù)據(jù)流量前所未有的增長。為了應對未來(lái)對數據帶(dài)寬的需求,PCI-SIG於2019年(nián)發布(bù)了(le)PCIe 6.0,將數據傳輸速率(lǜ)翻倍至64GT/s。最終版PCIe 6.0標準已於(yú)2022年1月正式(shì)發布。

IO帶寬增長預測和PCIe標準的演化(圖片(piàn):Cadence)

PCIe 6.0的主要挑戰

將I/O帶寬從PCIe 5.0的32GT/s翻倍至64GT/s給信號完整性(SI)帶來了巨大挑戰。PCIe向(xiàng)後兼容的需求(qiú)必須持續支持PCB、連接頭和擴展卡(kǎ)等傳統通道。數據速率為32GT/s且采用不(bú)歸零(líng)製(NRZ)編碼時,傳統通(tōng)道的插入損耗總和在奈奎斯特頻率(16GHz)下可達到36dB以上;當速率提升至64GT/s NRZ時,奈奎斯(sī)特頻率翻倍至32GHz,通道的頻率相關損耗將增加到70dB以上(shàng)。如此的全通道信號損失將令噪音(yīn)完全無法識別,傳(chuán)輸的數據將無法被有效還原。

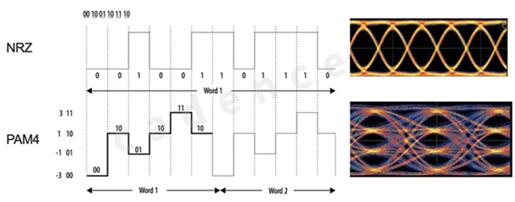

PAM4加持PCIe

將信號調製模式從非歸零編碼(mǎ)(NRZ)改至四電平脈衝幅度調製(PAM4)是PCIe 6.0克服通道信號損失(shī)挑戰的(de)方法。PAM4是一種多電平信號傳輸(shū)技術,每個單位(wèi)時間(UI)傳輸2比特,而(ér)NRZ每個(gè)單位時間僅傳輸1比特(見圖2)。采用(yòng)PAM4信號調製技術的PCIe 6.0每個UI可(kě)以(yǐ)傳輸2比特數據,數據速率(lǜ)在奈奎斯特(tè)頻率不變的(de)情況(kuàng)下增加一倍,成為PCIe 6.0的一大優勢。通道損失也因此與PCIe 5.0一樣可控。

PAM4信號調製(圖片:Cadence)

然而,升級至采用PAM4信號(hào)調製的PCIe版本還需要解決一係列挑戰,並應(yīng)對因此導致的複雜性上升。幸運的(de)是,Cadence對PAM4並不陌生。早在2017年,Cadence就通過(guò)對(duì)Nusemi公司的收購開始研發112Gb/s的PAM4技術。今天,Cadence已經是多個先進FinFET節點下(xià)112G/56G PAM4 SerDes IP的領先供應商,客戶使用我(wǒ)們的IP已經開發出多項成功的芯片設計。

協議更新,為效率(lǜ)而生

PIPE到控(kòng)製器的接口也升級到了6.0版本,延遲(chí)進一步降(jiàng)低。

PCIe 6.0標(biāo)準引入了流控製單元的概念(FLIT),與PAM4所需的前向糾錯(FEC)高效協同,為采用最常見配置的主流負載提供更低的延遲。

PCIe前代版本通過(guò)動態鏈路(lù)帶寬和低(dī)功耗狀態實現節能。但在此過程中,動態鏈路帶寬會幹(gàn)擾數據流的傳輸。PCIe 6.0采用全新的低功耗狀態L0p,可在不幹擾數據流的(de)前提下允許功耗相對帶寬(kuān)的(de)按比例調整。

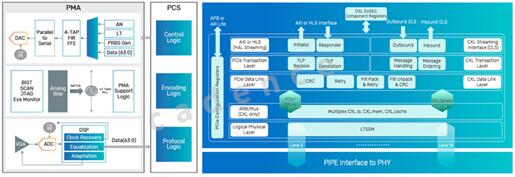

Cadence針對PCIe 6.0的完整IP解決方案(àn)

Cadence的PCIe PHY和控製器解決方(fāng)案(圖片:Cadence)

Cadence致力於引領(lǐng)行(háng)業采(cǎi)用最新的PCIe 6.0標準,用PCIe 6.0 IP解決方(fāng)案應對前沿領域快速變革的技術需求。過去20年,Cadence一直是PCIe PHY和控製(zhì)器的領先供應商。采用Cadence領先(xiān)的PAM4技術以及經過驗證的112G/56G PAM4以太網PHY IP,結合在PCIe領域深厚(hòu)的經驗,Cadence致力於為市場提供最先進的PCIe 6.0 PHY和控製器IP。

投稿箱(xiāng):

如果您有機床行業、企業相關新聞稿件發表,或進行資訊(xùn)合作,歡迎聯係(xì)本網編輯部, 郵箱:skjcsc@vip.sina.com

如果您有機床行業、企業相關新聞稿件發表,或進行資訊(xùn)合作,歡迎聯係(xì)本網編輯部, 郵箱:skjcsc@vip.sina.com

更多相關信息

業界視(shì)點

| 更(gèng)多

行業數(shù)據

| 更多

- 2024年11月 金屬切削機床(chuáng)產量數據

- 2024年11月 分地區金屬切削機床產量數據

- 2024年11月 軸承出口情況(kuàng)

- 2024年11月 基本型乘(chéng)用車(轎車)產量數據

- 2024年11月 新能源汽車產量數據

- 2024年11月(yuè) 新能源汽車銷量情況

- 2024年10月 新能源汽車產量數據

- 2024年10月 軸承出口情況

- 2024年10月 分地區金屬切削機床產量數據

- 2024年10月 金屬切削機床產量數據

- 2024年9月(yuè) 新能源汽車銷量(liàng)情況(kuàng)

- 2024年8月 新能源汽車產量數據

- 2028年8月 基(jī)本型乘用車(轎車)產量數據

博文選(xuǎn)萃

| 更多

- 機(jī)械(xiè)加工過程圖(tú)示

- 判斷一台加工(gōng)中心精度的幾種辦法

- 中走絲線切割機床的發展趨勢

- 國產數(shù)控係統和數(shù)控機床何(hé)去何從(cóng)?

- 中國的技術工人都去哪裏了?

- 機械老板做(zuò)了十(shí)多年,為何還是小作坊?

- 機(jī)械行業最新自殺性營銷,害(hài)人害己!不倒(dǎo)閉才(cái)

- 製(zhì)造業大逃亡

- 智能時代,少談點智(zhì)造,多談點製造

- 現實麵前,國人沉默。製造業的騰飛,要從機床

- 一文搞懂數控車床(chuáng)加工刀具(jù)補(bǔ)償功能

- 車床(chuáng)鑽孔攻(gōng)螺紋加工方法及工裝設計

- 傳統鑽削與螺旋銑孔(kǒng)加工工藝的區(qū)別